近日,思博伦通信宣布,将与Cadence Design Systems公司合作交付一种网络系统级芯片(SoC)验证解决方案,填补芯片流片前和流片后验证之间的空白。

这项合作将为Cadence Palladium® Z2企业级仿真和Protium™ X2企业级原型设计系统的流片前验证引入先进的以太网流量仿真和测试能力。凭借其极高的扩展能力和灵活性,该解决方案可以在应用层面上仿真从1G至800G的任意端口速度,并在需要时还可引入更多特性来实现全新的用例。

这项由思博伦和Cadence联合开发的解决方案的设计目标是,为验证数据中心和其它高性能芯片设计提供所需的高数据带宽。这项伙伴关系将思博伦TestCenter的高速率以太网的数据速率和端口密度,与Cadence Palladium和Protium系统在业界领先的验证能力融为一体, 创造出一种具备可重复使用、可迁移、可扩展自动化测试例的芯片流片前仿真测试解决方案。

思博伦云和IP部门负责产品管理的副总裁Aniket Khosla说:我们很荣幸能够与领先的计算软件厂商合作,通过这种高度灵活且成本效益显著的解决方案来填补下一代联网产品在流片前和流片后验证之间的空白。我们与Cadence的合作使我们获得接触最新的芯片设计验证解决方案的机会,可以帮助客户在设计周期的早期查明各类关键的问题,并加快最新创新的上市速度,为行业的发展注入动力。该解决方案将有助于缩短开发时间,简化复杂以太网芯片设计流程的测试,并确保新产品能够实现预期的性能。

Cadence公司系统和验证部高级产品管理事业部主管Michael Young表示:通过我们与思博伦的合作,Cadence将延续我们对业界领军企业的承诺,为流片前验证市场推出同级最佳的解决方案。当与Palladium仿真系统和Protium原型设计系统集成后,思博伦的以太网流量仿真和测试能力将帮助我们共同的客户利用真实世界的流量和场景大幅扩展其验证能力,进而缩短入市所需的时间。

该联合解决方案的独特优势包括:

(1)通过1G至800G的应用层面测试实现有效且高效的流片前验证测试。

(2)测试应用和仿真环境的全面集成,且无需使用任何外部测试硬件。

(3)在芯片设计的早期阶段便可查明和修复各类问题,从而节省大量的成本。

(4)可填补流片前和流片后验证之间空白的统一测试平台,实现从产品开发的最初阶段到客户部署的测试连续性。

(5)测试芯片产品生命周期所有阶段的能力、节省时间的应用重复利用、可实现更有效测试和结果分析的标准化指标实践,以及与CI/CD工作流程的简便集成。

(6)实现整个芯片开发生命周期的加速。

Aniket Khosla说:“芯片设计是一种时间密集型的活动,而在流片前设计阶段早期开展的测试可以减少开发周期后期可能遇到的问题和风险,有助于加快最新行业创新的上市速度。这种全新的统一测试平台能够降低测试的复杂性,并加快以太网芯片的技术设计和开发进程。”

亚信科技加入GTI合作伙伴领导委员会,推动全球5G产业创新发展

2023-09-11

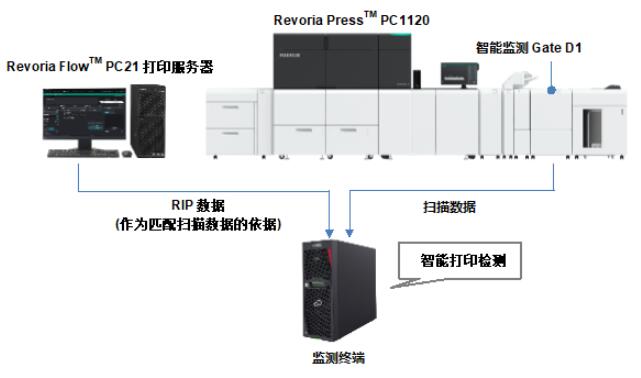

富士胶片商业创新推出Revoria Press PC1120智能检测系统

2023-04-12

Comviva推出CNPaaS用于通过网络API实现高级变现

2024-06-20

2024-07-19

2024-04-08

2024-06-18

2024-06-17

2024-03-07

2023-05-14

2024-03-04