(文/Suryash Rai,产品应用工程师)

问题

真正的无故障电压监控器IC存在吗?或者它只是一个概念?

回答

是的,真正的无毛刺监控器IC是存在的。MAX16161/MAX16162就是例子,即使在零电源电压下,这些IC也能产生可靠的复位信号,从而能够监控供电电压低于1V的电子器件。

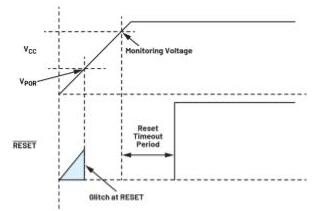

可靠的监控器IC始终是工业界的行业需求,因为它可以提高系统可靠性,并在电压瞬变和电源故障时提升系统性能。半导体制造商也在不断提高电压监控器IC的性能。为了生成明确或可靠的复位信号,监控器IC只需要一个称为上电复位的最低电压(VPOR),而在达到该最低电源电压之前,复位信号的状态是不确定的。一般来说,我们将其称之为复位毛刺。

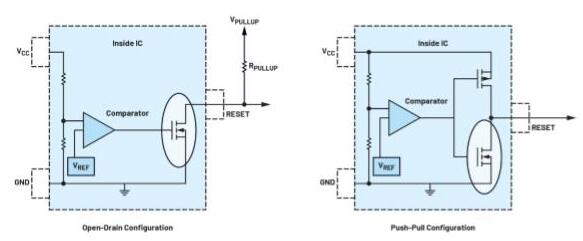

复位引脚主要有两种不同的拓扑结构:开漏和推挽(图1)。两种拓扑结构都使用NMOS作为下拉MOSFET。

上电期间,如果电源电压低于VPOR,就没有足够的电压能驱动内部MOSFET工作,因此MOSFET关闭。此时,监控器无法对复位电压进行控制。复位电压将与上拉电压(VPULLUP)成比例上升。而一旦电源电压高于VPOR,内部MOSFET将驱动RESET引脚进入有效状态。

图1.复位拓扑的开漏配置和推挽配置

图2.数据手册EC表中的POR规格

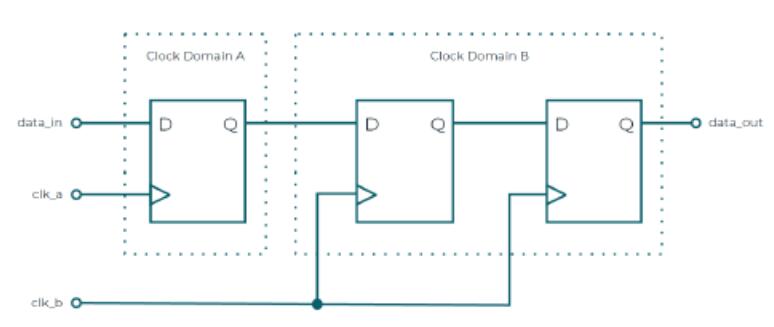

电压监控器可用于监控FPGA、ASIC或数字信号处理器的低电源轨,其电压可低至1 V。在低供电电压处理器中,I/O的逻辑电平非常敏感,其VIH可低至0.5 V,如图3所示。

上电期间,FPGA、ASIC或数字信号处理器需要处于RESET状态,直到所有电源轨稳定。当VCC低于VPOR时,RESET引脚可能会出现毛刺,该毛刺可能会触发FPGA的未知状态。一旦VCC高于VPOR,内部MOSFET就会开启,并将RESET连接到GND,使RESET引脚输出正确的逻辑低电平。

图3.监控器与低压ASIC、FPGA或数字信号处理器的接口

图4.带毛刺复位信号的上电时序

随着电子行业向低压半导体发展,模拟芯片制造商也在传统监控器的基础上努力实现无毛刺复位。制造商可以通过改进工艺来降低VPOR,但实现真正的无毛刺监控器需要一个全新的架构。

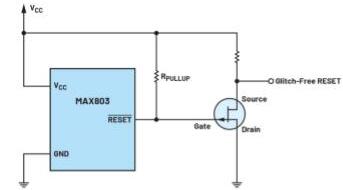

目前,如图5所示系统工程师使用带有传统监控器的外部电路来模拟无毛刺监控功能。添加一个配置为源极跟随器的标准JFET可以实现这一功能,源极的电压将取决于栅极电压VG与JFET阈值电压的差。JFET阈值电压会在VG和VOUT之间产生大约1 V的压降,从而避免监控器的输出电压在内部MOSFET关断时升高,直到监控器的内部MOSFET开始正常工作。

图5.带有外部P型JFET的传统监控器,可实现无毛刺工作

结论

真正的无毛刺监控器IC不再只是一个概念。设计人员现在拥有一款能在零电源电压下产生可靠复位信号的监控器IC,使系统工程师能够使用该IC来监控低供电电压(低于1 V)的电子器件。MAX16161/MAX16162为微型nanoPower IC,静态电流仅为825 nA,有助于延长系统电池寿命。

图6.MAX16162的应用示意图和相应的时序图

关于作者:

Suryash Rai自2016年以来一直在ADI公司担任应用工程师,负责支持保护IC产品组合。他拥有卡纳塔克邦国家技术学院的通信工程硕士学位。Suryash目前居住在加州圣何塞,爱好烹饪、旅行和交友。

2024-05-30

看见数智广东 | 推进信号升格 打造5G-A与低空经济产业高地

2024-03-22

2024-06-26

2022-11-30

2023-10-09

2023-04-06

盛思锐加入Connectivity Standards Alliance,塑造物联网智连未来

2023-05-22

2023-06-06

一举两得:支持双数据连接的全新第二代高通双卡双通释放5G蜂窝技术双连接的全部潜能

2023-05-31

将ASIC IP核移植到FPGA上——如何确保性能与时序以完成充满挑战的任务!

2024-08-26